Design Technology Co-Optimization

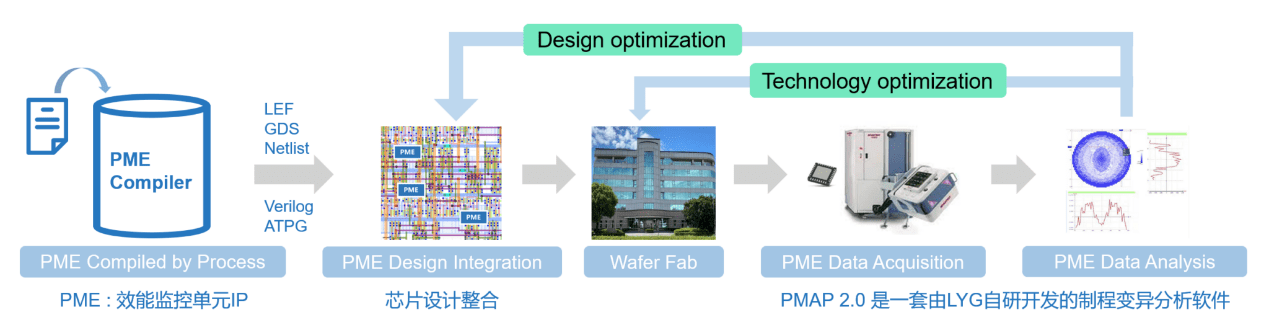

先进制程是指可以把晶体管尺寸做得更细小的制造技术,制造工序繁多且复杂,传统的晶圆切割道结构测试 (Wafer Acceptance Test, WAT) 以测量组件的电流与电压关系为主,只能监控组件的静态特性,但是这样的信息已不足够。随着先进制程的不断推进, 在过去依循的摩尔定律预测「晶片上面的晶体管数目在18个月到两年时间增加一倍。」也遇到了瓶颈,增加晶体管密度的代价高昂且能效优化的速度也开始趋缓慢。设计技术协同优化 (Design Technology Co-Optimization, DTCO) 可以是从工艺的视角出发往电路设计的方向进行优化,亦可由电路设计视角出发优化工艺的性能和效率。芯片设计者虽然可植入特殊电路以获取更多工艺相关的动态数据做为芯片效能的分析数据,而对于这些数据,传统的分析方法是使用制表软件与公式进行计算或绘图,严重依赖测试者的经验,可维护性差,也不便于管理,因此凌烟阁发展了效能监控分析系统 Performance Monitoring Analysis Platform, PMAP 2.0。

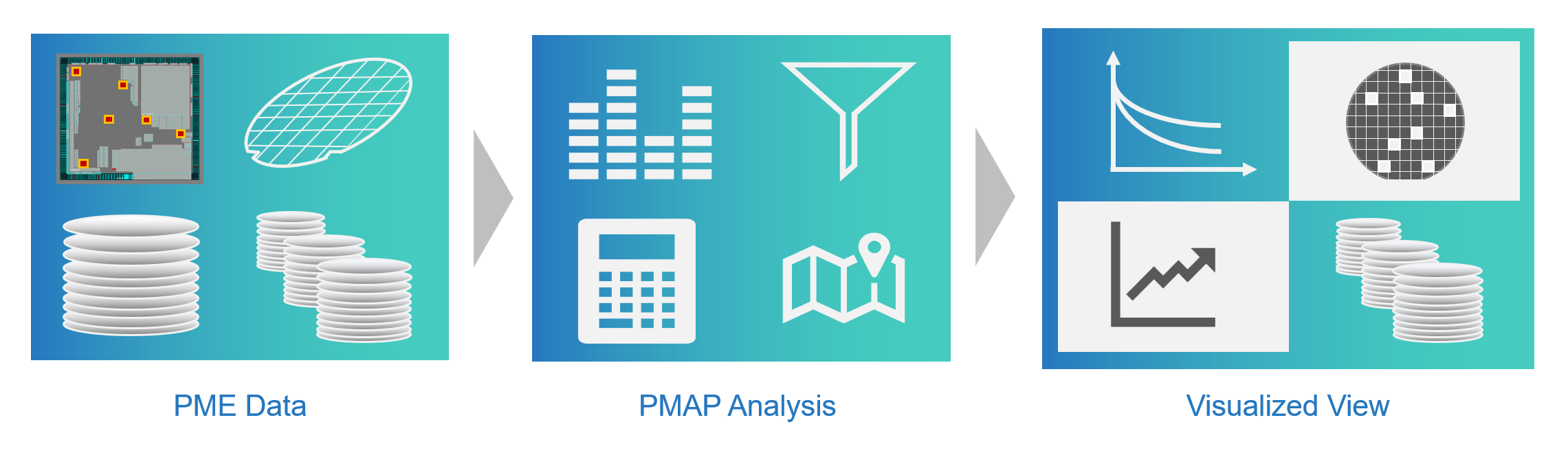

PMAP 2.0 由两个部件组成:第一个部件是效能监控电路,负责收集芯片操作时各项电性数据的硬件IP;第二个部件是数据分析平台,是对收集的数据进行存储,管理与分析的 EDA 软件解决方案。通过 PMAP 2.0 简化制程资料分析的工作,并且可以得到更多的芯片内部数据。

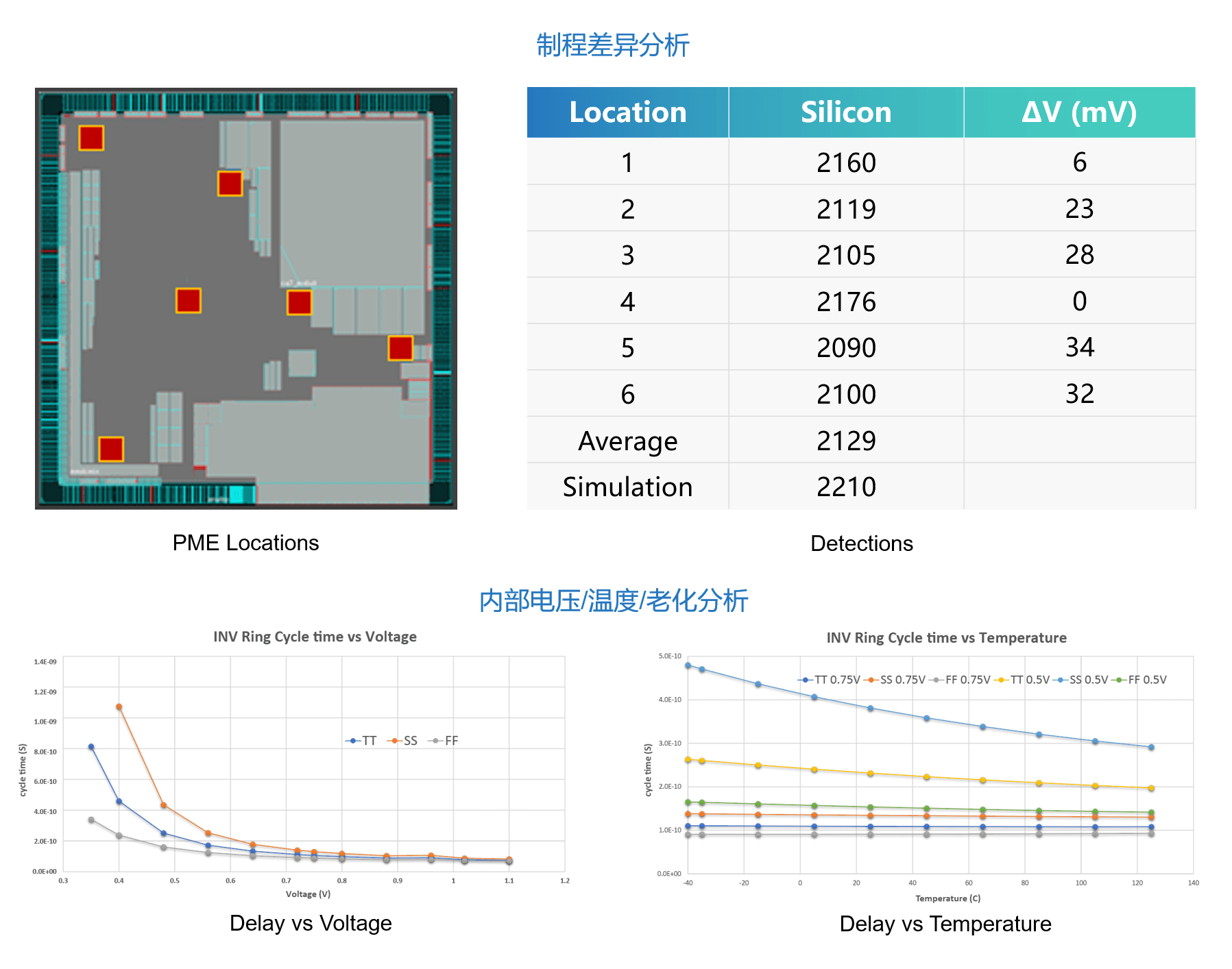

效能监控电路部件之所以重要,是因为晶圆厂会提供不同临界电压 (Threshold Voltage, VT) 的晶体管供客户选用。客户可以组合这些晶体管进行设计,以满足芯片的高效能和低功耗目标。在全面自动化的 PMAP 2.0 中,系统将自动产生效能监控电路来监控客户的设计,其中一种效能监控电路就是环形震荡器。

环形振荡器会被设定在某个频率操作,一旦制程、电压和温度不稳定,频率就会有所改变。所以如果环形振荡器展现的稳定性高且耗电小,代表有较优异的制程能力。因此可用来评估晶圆代工厂的优劣,也可做为芯片效能监控的电路,相对于晶圆切割道结构测试而言,它有更高的识别精度。

在我们的 PMAP 2.0 中的环形振荡传感器就有11种设计,分别使用不同的晶体管和逻辑门所构成,可以有效放大并量测不同晶体管的电性参数。我们期待 PMAP 2.0 可以作为 SoC 系统级芯片制程及设计交互改善的自动化解决方案,并提供客户高可靠度产品的使用效期监控之自动化解决方案。