Design Technology Co-Optimization

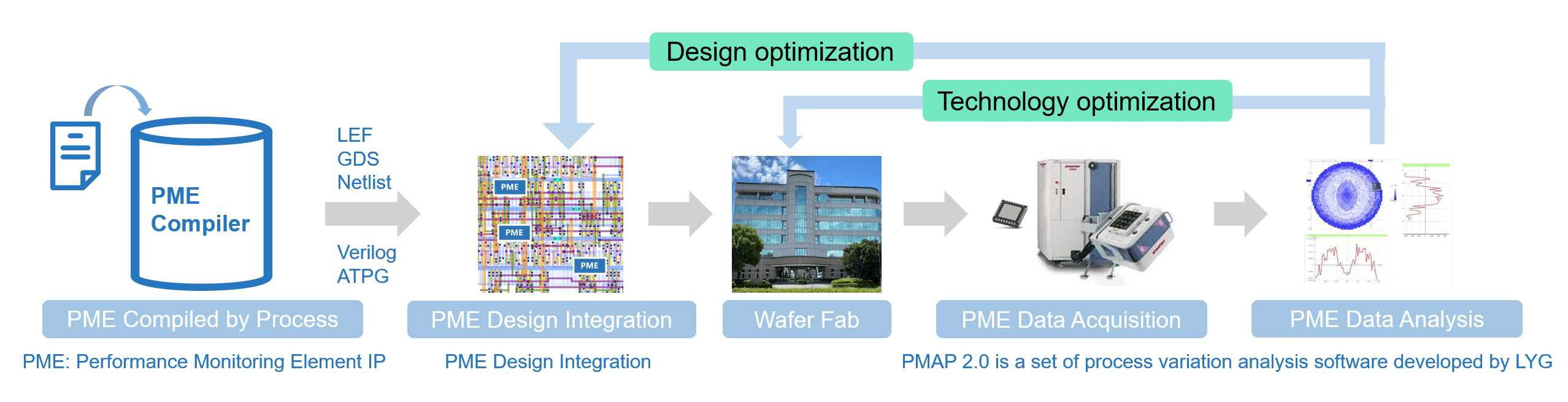

Advanced process technology refers to manufacturing techniques that allows for smaller transistor sizes. There are many and complex manufacturing processes. Traditional wafer acceptance testing (WAT) focuses mainly on measuring the current-voltage relationship of components and only monitors their static characteristics. However, such information is no longer sufficient. With the continuous advancement of advanced manufacturing processes, the previously followed Moore's Law prediction that "the number of transistors on a chip will double in 18 months to two years." has also encountered bottlenecks. The cost of increasing transistor density is high and the rate of energy efficiency optimization is slowing down. Design Technology Co-Optimization (DTCO) can optimize circuit design from the perspective of process toward circuit design, or improve process performance and efficiency from the viewpoint of circuit design. Although chip designers can implant special circuits to obtain more process-related dynamic data as analysis data for chip performance, the traditional analysis method is to use spreadsheet software and formulas for calculations or graphs, which relies heavily on the experience of testers. This approach has poor maintainability, and is not easy to manage. Thus, Lingyange developed a performance monitoring analysis system, Performance Monitoring Analysis Platform, PMAP 2.0.

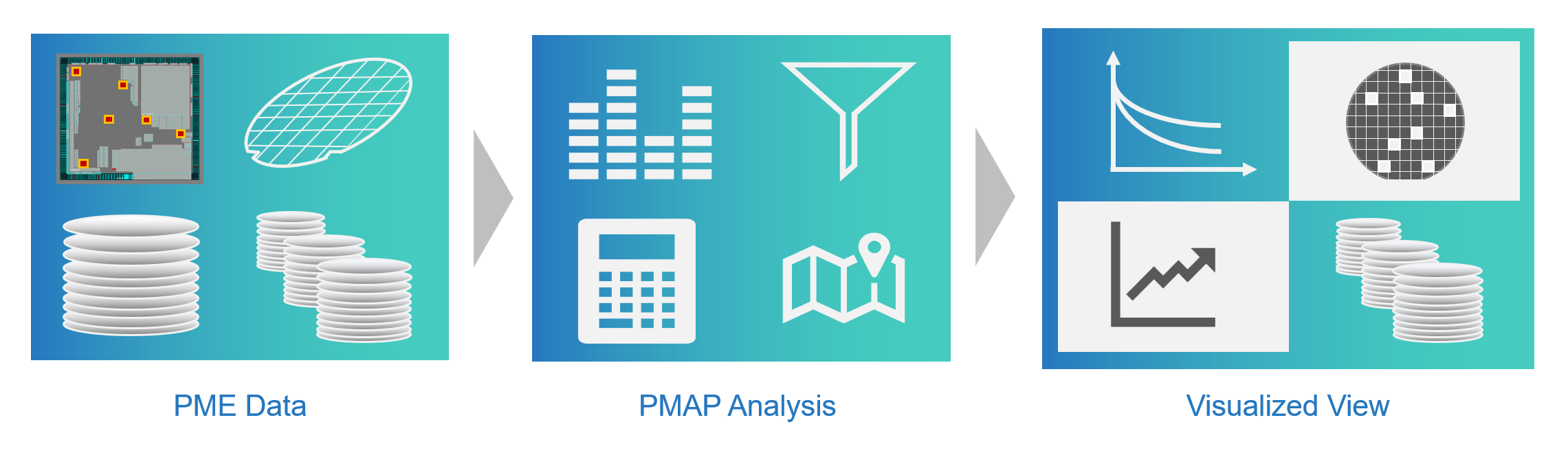

PMAP 2.0 consists of two components: the first component is the performance monitoring circuit, which is the hardware IP responsible for collecting various electrical data during chip operation; the second component is the data analysis platform, an EDA software solution that stores, manages, and analyzes the gathered data. PMAP 2.0 simplifies the analysis of process data and enables access to a more extensive set of internal chip data.

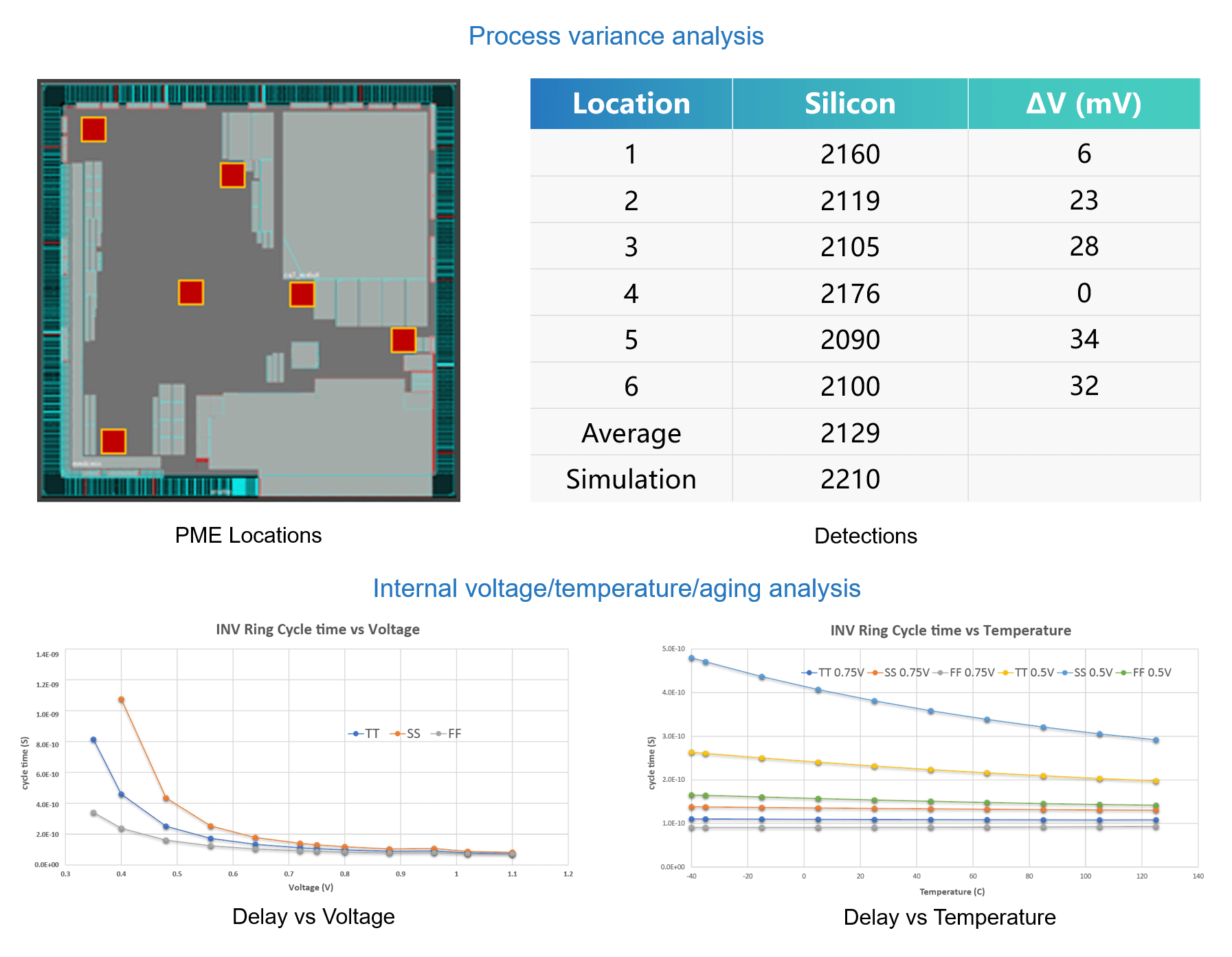

The importance of the Performance Monitoring Circuit component lies in the fact that semiconductor foundries provide transistors with different Threshold Voltages (VT) for customers to choose from. Customers can combine these transistors in their designs to meet the high-performance and low-power consumption goals of their chips. In the fully automated PMAP 2.0, the system automatically generates performance monitoring circuits to monitor customer designs. One such performance monitoring circuit is the ring oscillator.

A ring oscillator is set to operate at a certain frequency. Any instability in the process, voltage, or temperature will result in a change in frequency. Therefore, if the ring oscillator exhibits high stability and low power consumption, it indicates superior process capability. As a result, it can be used to assess the quality of semiconductor foundries and serve as a circuit for monitoring chip performance. Compared to Wafer Acceptance Testing, it offers higher identification accuracy.

In our PMAP 2.0, there are 11 different designs of ring oscillator sensors, each constructed using different transistors and logic gates. These sensors effectively amplify and measure the electrical parameters of various transistors. We envision PMAP 2.0 to serve as an automated solution for improving the interaction between SoC system-level chip processes and designs. Additionally, it aims to provide an automated solution for monitoring the usage lifespan of high-reliability products for our customers.