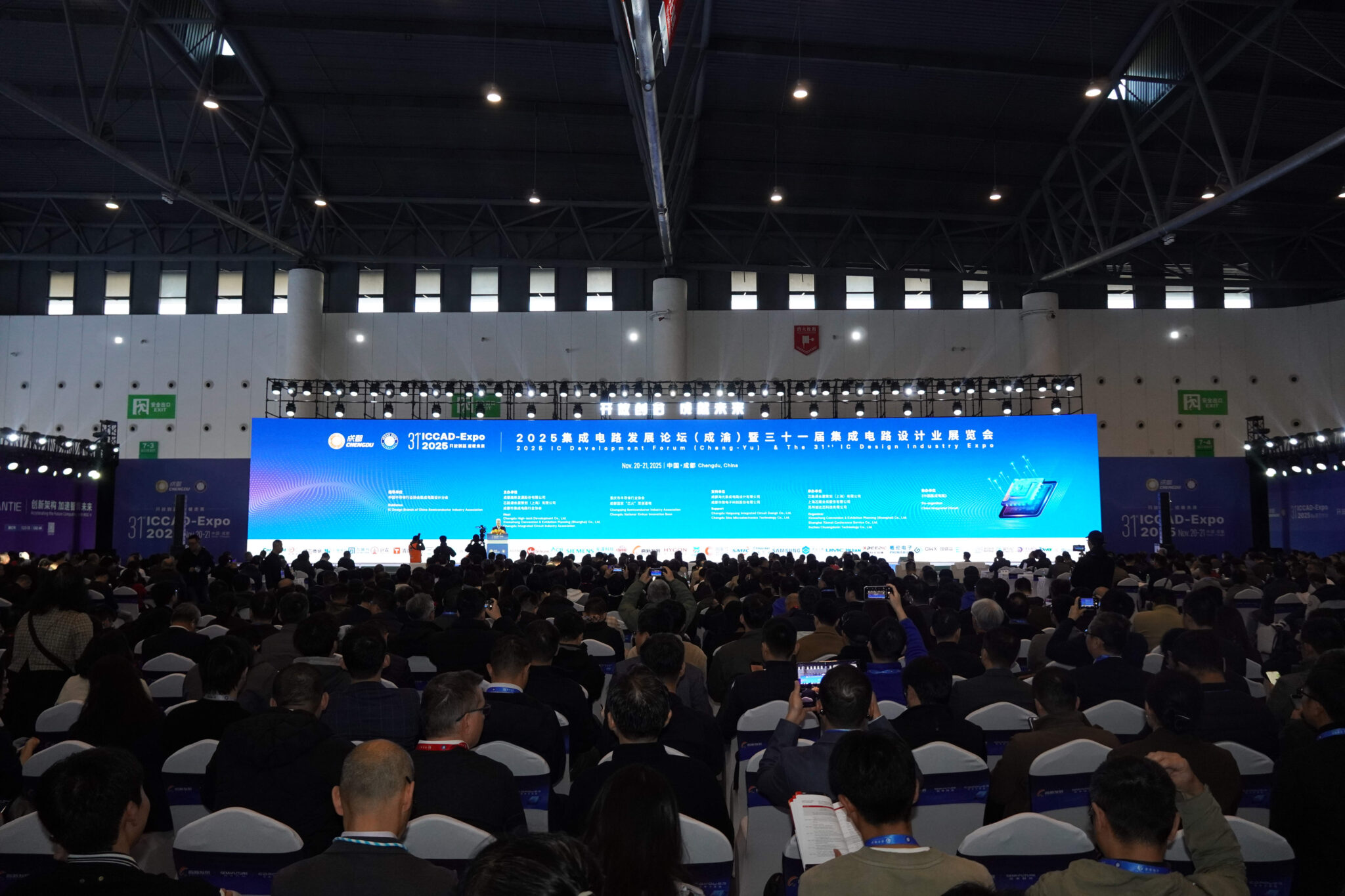

11月20-21日,2025集成电路发展论坛(成渝)暨第三十一届集成电路设计业展览会(ICCAD-Expo 2025)在成都・中国西部国际博览城盛大举行。凌烟阁芯片科技参加展会,积极推动“贞观”芯片设计流程标准化平台(DOP:Design Operation Platform)成为业界设计流程标准,提高芯片设计的劳动生产率。倡导DTCO(设计工艺协同优化)方法学,提升芯片的效能,进而提高终端产品的竞争力。通过现场展示及主题演讲,与全球行业伙伴共探集成电路产业发展新机遇。

作为国内集成电路领域的顶级盛会,本届 ICCAD 以“成渝同芯,同屏共振”为主题,汇聚300多家海内外领军企业与万名专业观众,覆盖 AI 芯片、先进工艺、EDA工具等核心热点。

凌烟阁此次参展,同步展示AI-SoC GPU 加速卡、AI-Edge Server 边缘运算伺服器、Magpie RISC-V MCU 等核心产品实物,集中呈现在高效能芯片设计、高可靠芯片开发验证及测试,芯片设计与工艺协同等领域的技术突破与实践成果,彰显本土芯片设计服务公司的硬核实力。专业团队全程为客商提供技术咨询与合作洽谈服务,助力行业伙伴精准对接需求,共拓合作新空间。

聚焦高效能、高可靠芯片设计开发,精准服务产业核心需求

高效能芯片设计AI-SoC:算力与能效的双重突破。针对 AI计算、高效能运算等核心场景,凌烟阁推出高性能 AI-SoC芯片设计方案。依托先进工艺(6nm/7nm)与深度优化的架构设计,该方案实现超高能效比,在加密货币、数据中心、5G SDR 等领域已取得多个成功案例。通过与客户从IP和单元库阶段深度合作,可在近临界电压操作下实现速度效能提升、功耗降低的优异表现,为AI时代的算力需求提供强劲支撑。

高可靠芯片开发验证及测试:全链路品质保障。凌烟阁构建了覆盖车用、工业、医疗等高端领域的高可靠芯片开发验证体系,遵循ISO 26262车用安全规范,提供从设计到量产的全流程测试解决方案。核心优势包括厚闸极氧化层单元库、双内栓塞单元库等高可靠IP,以及 SPAT/DPAT/GPAT 零缺陷率测试方案,可实现芯片在严苛环境下的稳定运行。同时,通过自研 PMAP 制程变异分析软件,实现芯片寿命预测与效能分级,为客户提供从原型验证到量产交付的全链路品质保障。

“贞观”设计流程标准化平台:提高芯片设计的劳动生产率

“贞观”平台作为凌烟阁自主研发的设计资源与自动化管理平台,五年磨一剑,已于近期正式对合作伙伴开放。

它是一套经过验证的可靠交付体系,实现项目资源智能调配与设计流程自动化管理。该体系贯穿项目规划、问题追踪、会议决策到IP复用,让项目进程清晰可视、风险精准可控、成本持续优化、交付坚实可靠。凌烟阁把芯片设计经验变成系统,把系统变成标准,让设计更快、更准、更稳,将大大提高芯片设计劳动生产率。无论是先进工艺芯片还是高可靠度专用芯片,贞观平台将提供灵活适配的标准化工具链与定制化解决方案,降低客户研发门槛。

DTCO 设计工艺协同优化:提升芯片效能、提高终端产品竞争力

在大会举办的 “IP与IC设计服务” 专题论坛上,凌烟阁研发副总吴烈铭将带来“先进设计服务 DTCO 与设计流程标准化平台”主题演讲,深入解析 DTCO 方法学在先进工艺中的应用实践与标准化平台的效率优势。

凌烟阁DTCO(设计工艺协同优化)方法学,颠覆传统芯片设计与制程开发的线性流程,在工艺研发阶段即实现设计与制程团队深度协同。通过自研 PME(效能监控单元 IP)与 AI 赋能的 Copernic 分析软件,精准把控设计余量与 OCV 变异,结合libMetrics工艺库分析工具,实现芯片性能、功耗与面积(PPA)的最优平衡。该技术已在先进工艺中得到验证,可助力客户实现速度提升、功耗降低的显著效益,为 HPC、AI等高端芯片提供核心竞争力。

此次 ICCAD 之旅,凌烟阁以技术为桥、以创新为翼,不仅展现了在芯片设计领域的深厚积淀,更传递了与行业共发展的坚定决心。

未来,凌烟阁将持续深耕DTCO 方法学等核心技术,推广“贞观”设计流程标准化化平台,不断迭代高效能 AI-SoC 设计方案与高可靠芯片验证体系,以更优质的产品与服务赋能全球客户。期待与产业链上下游伙伴携手,在集成电路产业的创新浪潮中并肩前行,为中国芯片产业高质量发展注入持久动力。