LYG's automotive microprocessor design reference platform, which includes digital core IP and highly reliable analog IP, can help customers develop vehicle safety projects and quickly reach mass production. According to the application scenario, the most suitable process and processor core can be selected, and the PUF security solution can be combined to strengthen the communication security of the Internet of vehicles.

The customized IP development of automotive microprocessors, from circuit design to chip function verification, complies with ISO 26262 specifications, and also meets the quality inspection standards of AEC-Q100.

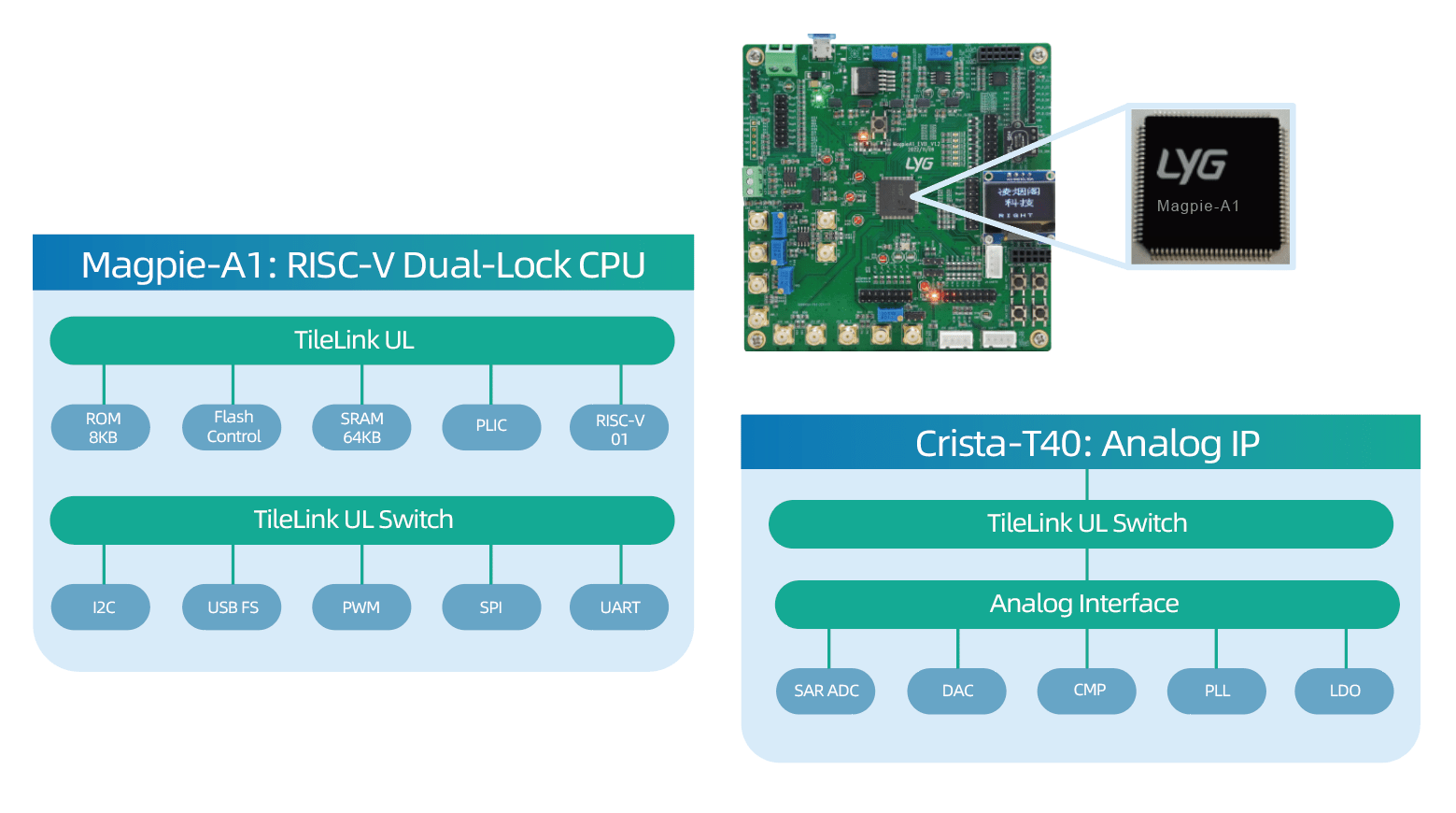

Automotive microprocessor chip development platform

Three major characteristics

01.Comply with ISO 26262 vehicle safety specifications, built-in dual-core lock step function, can execute the same code and strictly

02.Modular core and interface, customers can freely combine into the most suitable microprocessor chip.

03.High specification analog IP design, in line with the requirements of automotive and industrial microprocessors.

Modular automotive MCU platform

The modular design of RISC-V microprocessor and the modular design of custom analog IP can be combined and applied to a variety of scenarios.

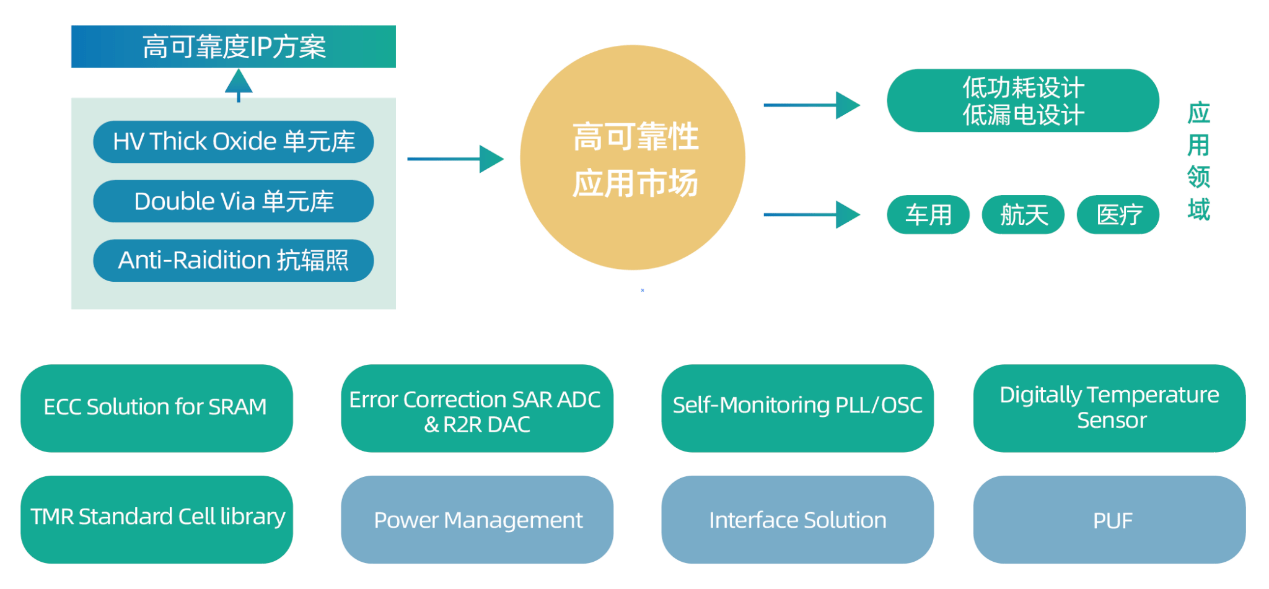

LYG self-developed IP

Automotive microprocessor development platform, LYG self-developed a variety of automotive IP, such as high-specification digital-to-analog conversion IP, accurate clock IP and a variety of high-reliability standard cell libraries.

High reliability standard component library

LYG provides a variety of high reliability standard component libraries to help customers develop products with special specifications.

The high thickness gate oxide standard cell (thick oxide standard cell) can save about 70% of the total power under the same operating frequency and operating voltage, and correctly apply the high thickness gate oxide standard cell library in the non-critical path or circuit block of the "always on" power domain. The leakage power of the chip will be reduced effectively.

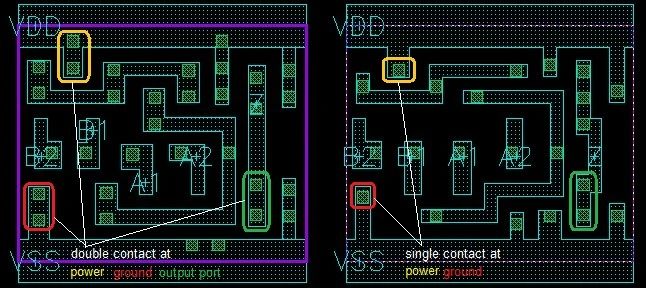

The use of double Con/Via standard cell can reduce the defects in chip manufacturing, further ensure the yield of chip manufacturing, suitable for high reliability chip products.

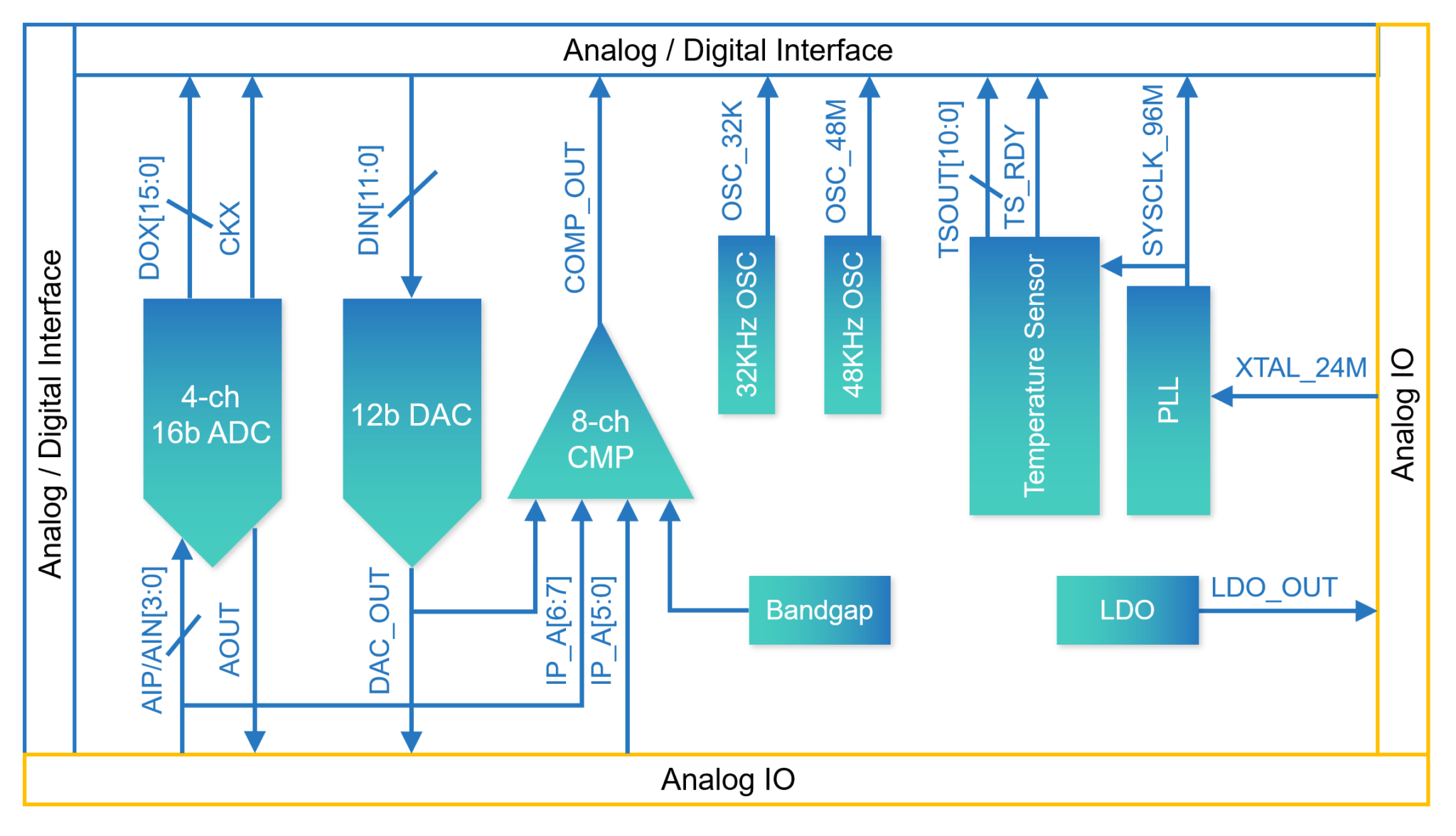

Customized Analog IP module

Feature List

• 4-ch 16-bit ADC

• 12-bit R2R DAC

• 8-ch Voltage comparator

• LDO regulator : 0.9~2.8V, 100mA

• Digital Temperature sensor : ±3˚ C

• PLL : 20MHz ~ 1.25GHz

• OSC1 : 32kHz

• OSC2 : 48MHz ± 1%

Digital-to-analog conversion circuits with various architectures (SAR, Sigma-Delta, R2R) and different accuracy (10~16 bits); Oscillator, PLL, DLL; Various power supply related IP (POR, LDO regulator, Bandgap reference); Fully digital temperature sensor.

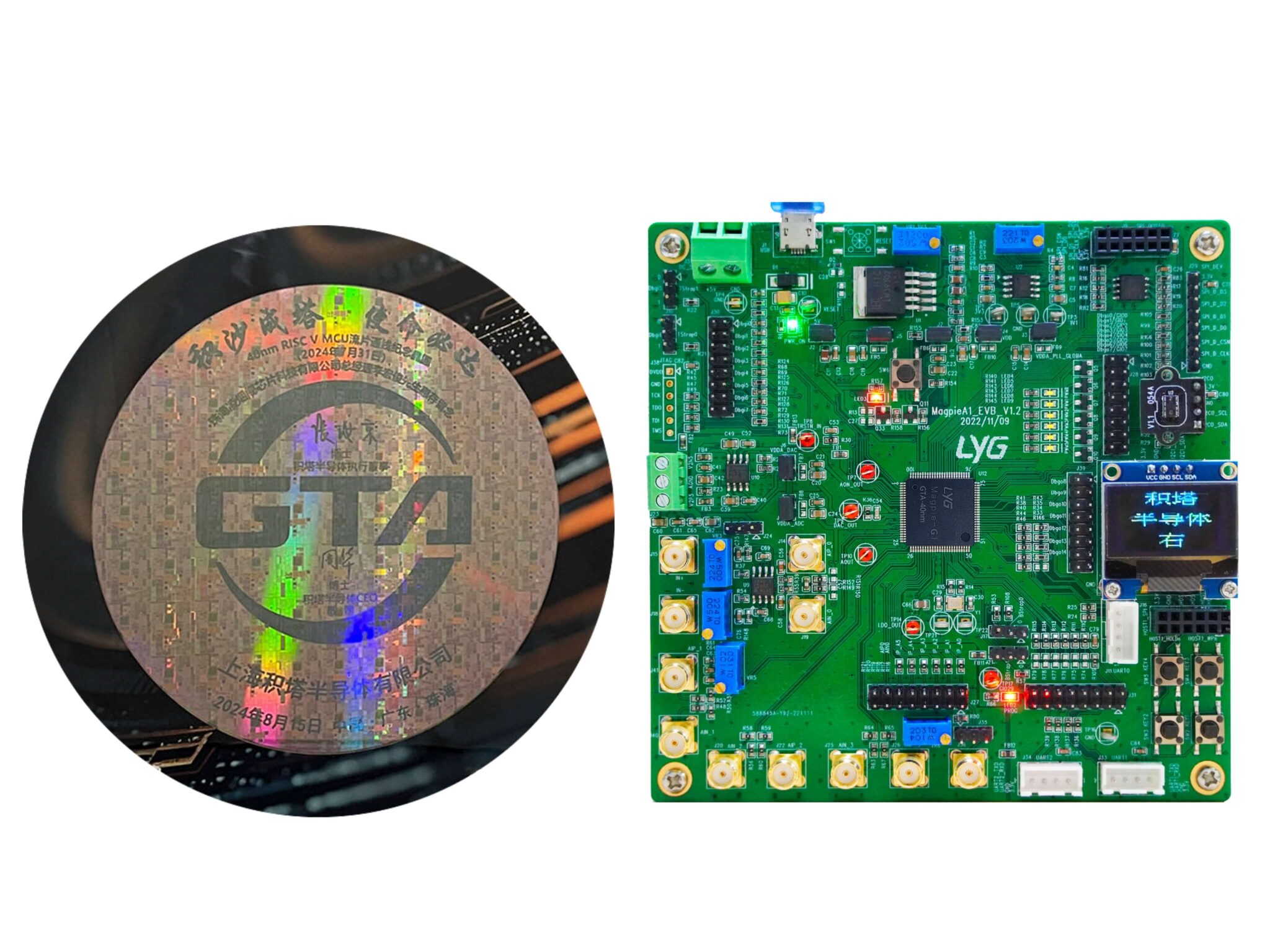

The above picture shows the Demo and verification environment on site. The 40nm microprocessor chip Magpie-A1 and the simulation IP have completed system verification.

LYG and GTA carry out strategic development cooperation to provide high-efficiency and low-power chip design solutions to meet the most stringent application requirements of MCU chips for high-efficiency, low-power and high-integration, and accelerate the development process of domestic characteristics. And in 2024, it verified the cooperation scheme of microcontroller chip (MCU) and related analog IP for 40nm low power process (GTA40nmLP).

Technical Advantage

The core of the organ. Modular designed IP provides customers with the flexibility to quickly convert different core platforms (ARM/RISC-V) to upgrade different processes.

With analog IP for a variety of uses, improve the functional integrity of customers' products.